# A New Time To Digital Converter In Temperature Measurement Using All Digital CMOS Architecture

# Dr.Murugan A<sup>1</sup>, Harini T<sup>2</sup>, Priya T<sup>3</sup>, Sindhuja SM<sup>4</sup>

<sup>1</sup>Professor, ECE, M.Kumarasamy College of Engineering <sup>2,3,4</sup> UG Scholar, ECE, M.Kumarasamy College of Engineering

#### ABSTRACT

In this article, computerized Integral Metal Oxide Semiconductor beat contracting temperature sensor (PSSTS) is proposed with higher territory productivity, improved precision. An all-advanced CMOS overwhelms a duration converter in estimation of temperature with optimized cost and less circuit complexity. Initially, an inverter-based temperature-detecting defer line produces width relative to total temperature (PTAT). At that point, a heartbeat contracting defer line (PSDL) with a blending plan (PMS) gauges the PTAT beat through beat contracting. The two postpone lines become zone productive when the channel length of semiconductors is long. Expectedly, the region proficient PSDL diminishes the time goal. Here a period-added beat or a temperature-detecting beat generator is proposed. A cyclic defer line (DL) with a temperature-detecting defer line (DL) and a contracting defer line (DL) becomes field proficient and has a large enough unique distance. In order to resolve the influence of the balance error and increases the precision the time subractor is considered. Moreover, refined circuits with on-chip alignment are normally embraced to accomplish extraordinary execution. Nonetheless, these circuits decline the zone and intricacy of shrewd sensors, which is reasonable for minimal effort frameworks. As a result, the exploratory outcomes demonstrate the region proficient and accomplishes improved exactness and high goal.

#### **1. INTRODUCTION**

Time to Digital (Computerized) converters are used to transfer data obtained over a period of time into a more complicated code. The basic requirements are lower cost, less force spread, and higher linearity. In this case, the best solutions for fulfilling these criteria are time converters that use the required loop. In a variety of cautious instrumentation schemes, electronic test instruments, and timing machines, a-list of time to digital is used. Structure of Framework on chip multifaceted design has extended on a very basic level that both the processor community think about well as the correspondence among these focuses, which makes examining these systems incredibly testing. A post-silicon endorsement stage is ordinarily significant for ensuring authentic system endorsement. Despite the customary focus on fragment value, endorsements experts have actually based on a correspondence driven explore theory to ensure the exactness of on-chip associations. An immense piece of investigate multifaceted design lies in favoring the association between the system parts.

#### 2. TIME TO DIGITAL CONVERTER

In electronic instrumentation and sign setting up, an opportunity to cutting edge converter (TDC) is a device for seeing events and giving a modernized depiction of the time they occurred. For example, a TDC may yield the hour of appearance for each moving toward heartbeat. A couple of utilizations wish to evaluate the stretch of time between two events rather than some thought about a level out time. In equipment time-to-cutting edge converters (TDCs) or time digitizers are contraptions customarily used to evaluate a period range and convert it into modernized (twofold) yield. Occasionally embedding TDCs are similarly called time counters (TCs).

TDCs are used in a wide scope of employments, where the time frame between two sign pulses (start and stop beat) should be settled. Assessment is started and ended, when either the rising or the falling edge of a sign heartbeat passes a set limit. These requirements are fulfilled in various real assessments, like period of-flight and lifetime assessments in atomic and high energy material science, investigates that incorporate laser going and electronic investigation including the testing of composed circuits and high speed data move.

They are often used as the primary component of advanced processors, and for the ultrasonic heating meter industry, there is an additional temperature (evaluation) device on a nearby chip. A TDC with a heat deciding cutoff is needed by a robotized driving system and modern powered driven device. Two or three excellent thinking techniques, such as time increment, time (stage) development, and the Vernier rule, have been debated in order to achieve a high level for TDCs. Without a stupefying circuit, the beat contracting strategy was familiar enough to accomplish a sub doorway target. The technique can also benefit CMOS time-space informative temperature sensors. Since the sub passageway time objective can be effectively defined using beat contracting time estimation, beat contracting STSs are easily validated and have a low circuit intricacy.

# **3. LITERATURE SURVEY**

C.- C. Chen el. at [1] all-progressed CMOS (Corresponding Metal-Oxide Semiconductor) beat contracting sharp temperature sensor (PSSTS) is proposed to pass on the advantages of an area viability, improved exactness, and significant standard. Introductory, an inverter-based temperature-recognizing concede line delivers a heartbeat with a width comparative with preeminent temperature (PTAT). By then, a heartbeat contracting concede line (PSDL) with a heartbeat mixing plan (PMS) measures the PTAT thump through thump contracting.

By then J.- C. Lai [2] proposes a period development input intend to change objective and complexity in a cell-based TDC. The time development is strengthened and dealt with again into a cyclic-ring Vernier recursively until it can't be perceived precisely. Simply a solitary variable-objective cyclic-ring Vernier and one tunable deferral chain time speaker (TA) are embraced. Both coarse and fine oscillators of the proposed Vernier which are arranged by a comparable variable-objective modernized controlled oscillator (DCO) can be killed to reduce ground ricochet during TA works out. With various control codes, the TDC objective is moreover programmable.

P. Chen [3], significant standard TDC completed with field programmable doorway display (FPGA) considering concede wrapping and averaging is presented. The focal idea is to pass a lone clock through a movement of concede segments to make various reference tickers with different stages for input time quantization. In view of periodicity, those stages will be relatively wrapped inside one reference clock period to achieve the important fine objective. Before long, a mutt concede lattice is made to inside and out decline the important number of defer cells. Various TDC focuses are created for equivalent assessments and subsequently amazing coordinating control and averaging are applied to smooth out the gigantic quantization botches achieved by the inhomogeneity of the TDC delay lines for both linearity and single-shot precision update.

K. Cui el at [4], TDCs using gave pass on chains of FPGAs are for the most part planned in tapped-delay-line type which are genuinely researched lately. At any rate this strategy achieves vulnerable differential nonlinearity (DNL) which rises out of the normal unbalanced compartment granularity. This paper proposes a TDC designing which utilizes the pass on chains in an exceptionally one of a kind method to alleviate this long-standing issue. Two free pass on chains working as the concede lines for the fine time expansion are composed in a ring-oscillator-based Vernier style and the time contrast between them is finely changed by dispensing unmistakable number of essential defer cells. A specific arrangement stream is depicted to procure the ideal delay contrast.

C. C. Chen [5] presents a productive time-space CMOS wise temperature sensor with only one concede line. With the usage of a way decision circuit, the concede line was used to at first distinguish the temperature, to deliver a heartbeat with a width relating to incomparable temperature (PTAT). The first defer line was then reused to evaluate the PTAT beat. Last progressed code change was fulfilled using a direct counter. Stood out and past work from two concede lines, the proposed work with the novel plan can diminish one delay line to cut down the circuit zone [6,7,8,9,10].

# 4. EXISTING SYSTEM

The normal structures with self-checking TSC that experiences the difficulties as follows:

a) Implementing the whole circuit through uncommonly delegated plan for TSC;

b) Duplicating helpful squares and affirming the yield of these squares using a TSC data take a gander at framework through exceptionally named plan.

Approach (a) has shortcomings in which all of the circuits ought to be as of late arranged and did in an improvised cycle with incredibly serious arrangement impediments. Of course, approach (b) can engage the headway of TSC reasoning, anyway if the data examine part has an uncommonly named plan for shield; with everything taken into account, a normal arrangement of commonsense square can be easily used for a duplicate utilitarian square. Thusly, headway cost and time can be phenomenally diminished [11,12,13,14,15].

# 5. PROPOSED SYSTEM

Time to Advanced converters (TDCs) change the time contrast between two events into an automated regard and essential sections in various applications [16,17,18,19,20]. One of the crucial vocations of a TDC is On schedule of-flight assessments used in position spread tomography; space mechanical assembly laser altimeters, fluorescence lifetime imaging microscopy, laser edified revelation and going, and object arranging structures, among others. Since ToF tests measure the time required for the signs released from the goal to show up at the marker, TDCs with wide information reach and significant standard are principal.

Totally selfchecking (TSC) comparators with an internet inadequacy mixture strategy for intra chip abundance. These TSC comparators can act end with no change in the utilitarian squares, i.e., applying encoding, for instance, bumble cure code (ECC), to the helpful square. This decreases both improvement cost and the arrangement period for making LSIs. Another concern is that a static sporadic access memory (SRAM)- based FPGA is exposed against sensitive missteps achieved by a single event upset (SEU) with respect to radiation of endless pillars. Particularly, neutrons are seen as a critical justification sensitive errors for microelectronics on ground [21,22,23].

A FPGA for Rad-Hard is open, anyway this sort of FPGA is for exceptional use; consequently, the availability accessible is amazingly confined. We will probably use the standard business immediately available (Bunks) FPGAs for significantly reliable structures. To develop such a system, a strategy for reducing this issue deliberately and quantitative certification of the effect of SEU are central.

To achieve a broad standard for the Converters, a few eminent viewpoints, such as time improvement, time (stage) extension, and the Vernier law, have been discussed. The beat contracting solution did not involve an abnormal circuit, and the production team was familiar with achieving a subgate target.

The technique is often used for time-space sharp temperature sensors. Since the subgate time goal can be defined using beat contracting time evaluation, the beat contracting STSs can be upheld with minimal effort and have a low circuit diverse nature [24,25,26].

- 1. In view of the comparative advancements of heartbeat contracting TDCs and STSs, a TDC with temperature-evaluating limit is orchestrated in this assessment.

- 2. By utilizing a fundamental alteration on a sometime prior masterminded TDC.

- 3. To build circuit respect and save circuit cost, a single processor can make time-to-bleeding edge and temperature-to-electronic improvements.

- 4. The all-advanced CMOS configuration was used to reduce exertion while speeding up the final plan strategy.

# 6. PROPOSED BLOCK DIAGRAM

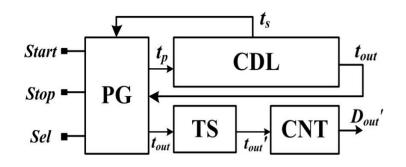

#### Fig.1 Proposed Block Diagram

The use of the required time subtractor, and a clock are included in the proposed TDCs, as seen in Fig.1. As contrasted to the Pulse Generator, the proposed TDCs' activities and development are indistinguishable from those of already masterminded heartbeat contracting TDCs. To reduce the impact of the harmony bungle and add a temperature monitoring limit without needing a more complicated circuit design and expense, the suggested PG is used to bypass the underlying go through snake. In the complementary metal oxide semiconductor inverter entryway, allowing for a longer channel length improves their area suitability and amazing range. Through the use of the more L, the all-motorized beat blending device in the cdl was able to create a worthy time objective. Finally, the time subractor is used to solve the harmony botch problem and achieve D with greater precision. It's the simplest single converter for conducting time-to-automated and temperature-to-bleeding-edge shifts.

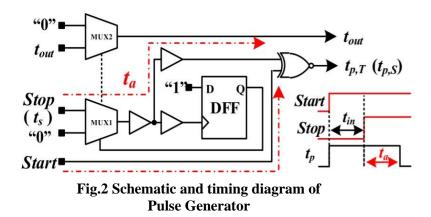

#### A. PULSE GENERATOR

The circuit and timing diagram for the PG The PG was used to make a loop applied beat (tp,T) or a temperature recognize beat (tp,S) (temperature-to-beat transition) for the TDC work, as well as to modify the two-stage change (beat age and time appraisal). TDC stands for "to the full degree possible". The PG can be compared to the time snake in which is responsible for the balance goof's influence. As seen by the specked line in the Fig. 2. the extra time ta is the result of the extra postponement of a yield chain and a multiplexer (MUX1) tp,T is the same as tin + ta, which is used in the CDL to measure timechange. Turning on the D-type flip-flop (DFF), which causes Mux1 and Mux2 to only move "0" and "advance," selects the lower technique for the two Mux's. Mux2 uses cyclic shrinkage of the beat in the CDL to measure advance to the TS. When major, a second concede chain should be fused to the ta way to ensure that the ta is greater than for the peace mess to break.

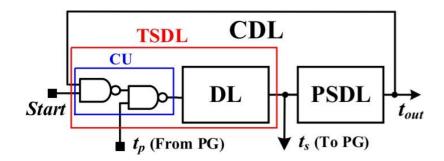

# **B. CYCLIC DELAY LINE**

The proposed TDC's Cyclic Delay Line consists of a Temperature Sensing Delay Line and a heartbeat contracting concede line, with the Temperature Sensing Delay Line providing a coupling assembly, with the gates and the gate used as is the NAND gate and then also consider an inverter based line to detect the amount of temperature that produced by temperature sensing for fast temperature-assessing limit identification.

International Journal of Modern Agriculture, Volume 10, No.2, 2021 ISSN: 2305-7246

The temperature-perceiving principle of the inverter-based delay line. They are expected to play a key rolein the transition from one time measurement to another. The intentional heartbeat tp was added to the cyclic delay thread by the control unit for cyclic heartbeat contracting time assessment. A longer L was assumed to be a zone effective and wide-cyclic delay line. In any case, the lower the target is the more L.

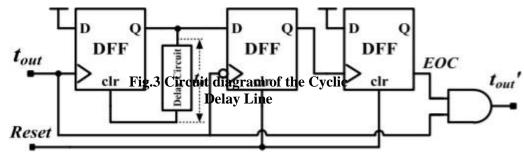

#### **C. TIME SUBRACTOR**

Fig.4 Circuit diagram of the Time Subractor

Then beat width is elevate was recognized to choose if the beat was more broad or more modest than ta. Right when the contracting width of the elevate ended up being not actually that of ta, the completion of progress (EOC) was started through the AND entryway to get t out as the yield. Basically, with the TS, ta was deducted and simply the ideal tin (=tp –ta) was completely changed over for the last progressed yield. The undesired equilibrium mix-up can be sufficiently discarded to improve precision

#### D. TEMPERATURE MEASURING CAPABILTY

The proposed TDC would merely be updated to include a security temperature-assessing limit in terms they want in need of high circuit. If time to digital converter needed temperature or acclimation to update the required precision, the Smart temperature sensor mode will provide it. Here we want to implement a additional sensor that is temperature sensor which is unlikely to lower the average cost of the circuit. This thought applies to a variety of circuits that need temperature separation in order to increase circuit motivation while reducing costs.

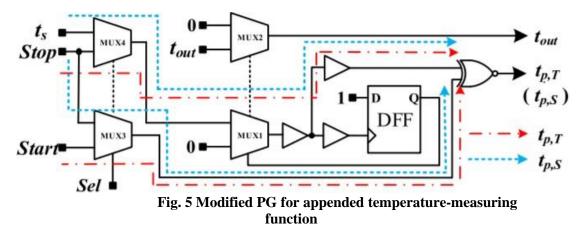

The addition of two Mux's (Mux3 and Mux4) to the critical Pulse Generator results in a major difference, as seen in Fig. 5. Differentiating forms for the time to digital converter in the extra Multiplexer, Multiplexer 3 in this pulse generator, and smart temperature control constraints in the extra Multiplexer, Multiplexer 3 in this pulse generator are implemented in the new pulse generator. Multiplexer, Multiplexer 4 and field has shown the performance of the TDC work (tp,T).

#### 7. RESULTS AND DISCUSSION

The all-Advanced CMOS TDC with temperature-evaluating boundary was built on a TSMC 0.35-µm CMOS scale. A chip microphotograph with its floor plan is shown in Fig .1. 0.019 mm is the usual middle position. The starter game-plan for the intended circuit, as seen in Fig. A. A Stanford Discovery DG645 electronic delay/beat generator was used to build the test signals Start and Finish. As a consequence, the information time frame was established (tin). The TDC was given a time stretch creation with widthsranging from 1 to 40 ns for execution testing. The suggested circuit is the most effective and has the greatest DR circuit a territory for the newly discovered TDCs Since a single Cyclic delay line for a longer length is used, the two redesigns are inevitable. Evaluation information was placed in the center of each data stretch to minimize the volume of data gathered due to optional time jitter.

# A. EXISTINGSYNTHESISREPORT

| Device Utilization Summary (estimated values) |                  |                   |               |

|-----------------------------------------------|------------------|-------------------|---------------|

| Logic Utilization                             | Used             |                   | Available     |

| Number of Slices                              |                  | 3                 | 960           |

| Number of Slice Flip Flops                    |                  | 5                 | 1920          |

|                                               | Device Utilizati | on Summary (estin | nated values) |

| Logic Utilization                             | Used             |                   | Available     |

| Number of Slices                              |                  | 3                 | 960           |

| Number of Slice Flip Flops                    |                  | 4                 | 1920          |

| Number of 4 input LUTs                        |                  | 5                 | 1920          |

| Number of bonded IOBs                         |                  | 9                 | 66            |

| Number of GCLKs                               |                  | 1                 | 24            |

# 8. CONCLUSION

The suggested circuit eliminates the need for a full-custom CMOS configuration by using cuttingedge CMOS thinking techniques. The suggested PG can be used to correct balance mistakes for precision improvement and to guarantee the temperature-surveying cutoff. It took me a while to figure it out. Allowing for a longer channel length increases area capability and increases DR. To achieve an outstanding time goal, an all-electronic beat blending system is used. According to preliminary results, the proposed study is feasible. The examination that can deliver a region and force data saves multimodal recognize costs without the need for additional hardware as opposed to previous TDCs or brand new circuits.

# REFERENCE

- [1] C.-C. Chen, C.-S. Hwang, and C.-S. Chu, "Area-efficient all-digital pulse-shrinkingsmart temperature sensor with improved accuracy and resolution," Rev. Sci. Instrument.,vol.89, no. 12, pp. 125002-1–125002-9, Dec. 2018

- [2] J.-C. Lai and T.-Y. Hsu, "Cost-effective time-to-digital converter using time-residuefeedback," IEEE Trans. Ind. Electron., vol. 64, no. 6, pp. 4690–4700, Jun. 2017.

- [3] P. Chen, Y.-Y. Hsiao, Y.-S. Chung, W.-X. Tsai, and J.-M. Lin, "A 2.5-ps bin size and 6.7-psresolutionFPGAtime-to-digitalconverterbasedondelaywrappingandaveraging," IEEE Trans. Very Large Scale Integrator. (VLSI) Syst., vol. 25, no. 1, pp.114–124, Jan.2017.

- [4] K. Cui, Z. Ren, X. Li, Z. Liu, and R. Zhu, "A high-linearity, ringoscillator-based, Verniertimedigital converterutilizing carry chains in FPGAs," IEEE Trans. Nuclear. Sci., vol. 64, no.1, pp.697–704, Jan. 2017

- [5] C.-C. Chen and H.-W. Chen, "A low-cost CMOS smart temperature sensor using athermal-sensing and pulse-shrinking delay line," IEEE Sensors J., vol. 14, no. 1, pp.278–284, Jan.2014.

- [6] R. B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P. T. Balsara, "1.2 V 20 ps time-todigital converter for RF frequency synthesis in 90 nm CMOS," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 3, pp. 220–224, Mar. 2006.

- [7] W. Pan, G. Gong, and J. Li, "A 20-ps time-to-digital converter (TDC) implemented in field-programmable gate array (FPGA) with automatic temperature correction," IEEE Trans. Nucl. Sci., vol. 61, no. 3, pp. 1468–1473, Jun. 2014.

- [8] J.-C. Hsu and C. Su, "BIST for measuring clock jitter of chargepump phase-locked loops," IEEE Trans. Instrum. Meas., vol. 57, no. 2, pp. 276–285, Feb. 2008.

- [9] Time-to-Digital Converter With Integrated Analog Front-End, TDCGP22, AMS AG, 2014.

- [10] Time-to-Digital Converter With Analog Front-End, MAX35101, MAXIM INTEGRATED, 2015.

- [11] J.-C. Lai and T.-Y. Hsu, "Cost-effective time-to-digital converter using time-residue feedback," IEEE Trans. Ind. Electron., vol. 64, no. 6, pp. 4690–4700, Jun. 2017.

- [12] P. Chen, Y.-Y. Hsiao, Y.-S. Chung, W.-X. Tsai, and J.-M. Lin, "A 2.5-ps bin size and 6.7-ps resolution FPGA time-to-digital converter based on delay wrapping and averaging," IEEE Trans. Very Large Scale Integrator.(VLSI) Syst., vol. 25, no. 1, pp. 114–124, Jan. 2017.

- [13] K. Cui, Z. Ren, X. Li, Z. Liu, and R. Zhu, "A high-linearity, ring oscillator-based, Vernier time-todigital converter utilizing carry chains in FPGAs," IEEE Trans. Nuclear. Sci., vol. 64, no. 1, pp. 697–704, Jan. 2017.

- [14] R. Szplet and K. Klepacki, "An FPGA-integrated time-to-digital converter based on two-stage pulse shrinking," IEEE Trans. Instrum. Meas., vol. 59, no. 6, pp. 1663–1670, Jun. 2010.

- [15] J. Zhang and D. Zhou, "An 8.5-ps two-stage Vernier delay-line loop shrinking time-to-digital converter in 130-nm flash FPGA," IEEE Trans. Instrum. Meas., vol. 67, no. 2, pp. 406–414, Feb. 2018.

- [16] T. Iizuka, S. Miura, R. Yamamoto, Y. Chiba, S. Kubo, and K. Asada, "A 580 fs-resolution time-todigital converter utilizing differential pulseshrinking buffer ring in 0.18 μm CMOS technology," IEICE Trans. Electron., vols. E95–C, no. 4, pp. 661–666, 2012.

- [17] C.-C. Chen, C.-S. Hwang, K.-C. Liu, and G.-H. Chen, "CMOS timeto-digital converter based on a pulse-mixing scheme," Rev. Scientific Instrum., vol. 85, no. 11, pp. 114702-1–114702-9, Nov. 2014.

- [18] C.-C. Chen, C.-S. Hwang, Y. Lin, and G.-H. Chen, "Note: Alldigital pulse-shrinking time-to-digital converter with improved dynamic range," Rev. Sci. Instrum., vol. 87, no. 4, pp. 046104-1–046104-3, Apr. 2016.

- [19] C.-C. Chen and H.-W. Chen, "A low-cost CMOS smart temperature sensor using a thermal-sensing and pulse-shrinking delay line," IEEE Sensors J., vol. 14, no. 1, pp. 278–284, Jan. 2014.

- [20] C.-C. Chen, C.-S. Hwang, and C.-S. Chu, "Area-efficient all-digital pulse-shrinking smart temperature sensor with improved accuracy and resolution," Rev. Sci. Instrum., vol. 89, no. 12, pp. 125002-1–125002-9, Dec. 2018.

- [21] C.-C. Chen, S.-H. Lin, and C.-S. Hwang, "An area-efficient CMOS time-to-digital converter based on a pulse-shrinking scheme," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 3, pp. 163–167, Mar. 2014.

- [22] P. Chen, S.-L. Liu, and J. Wu, "A CMOS pulse-shrinking delay element for time interval measurement," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 47, no. 9, pp. 954– 958, Sep. 2000.

- [23] Mohanraj, S. and M. Maheswari, 2011. "SERF and Modified SERF Adders for Ultra Low-power Design Techniques," Proc. Int. Conf. on Communication Technology and System Design. Published by Elsevier Ltd, pp: 639-645

- [24] Pradeep.S et al.. (2019). Design and Implementation of Fault Tolerant Hybrid Full Adder Using Inverter. International Journal of Advanced Science and Technology, 28(17), 653 659.

- [25] Janani .M,Janaki.K, 2019. Multiplier Based on BST for High-Performance Compression. International Journal of Control and Automation. 12, 6 (Dec. 2019), 246 - 255.

- [26] Aathilakshmi S. et al.. (2019). An Efficient VLSI Multiplier Design For Signal Processing. International Journal of Advanced Science and Technology, 28(13), 308 - 320.